ASM Diaries 4: Don’t Optimise Error Paths

This piece should really be called ‘optimise the path which is not the error path’ but that’s a very unsexy title. The point here is that your code’s error path is (usually) executed a single time before returning to the user for input. That says that it’s not time-sensitive and you don’t need to optimise …. Read More

ASM Diaries 3: Eliminate Jumps by Pre-loading

Writing the code to validate ranges in type definitions in Quiche-Z80 I needed to test for some values. I could easily handle the cases where both values where unsigned or both values where signed but the case where one was signed and the other unsigned allowed a nice little optimisation. Due to the typing rules …. Read More

ASM Diaries 2: A Hack for Case Insensitive Identifiers

This article will make a lot more sense with an ASCII table to look at. I don’t have quick access to a copyright free one, but you view one at https://www.asciitable.com Case insensitive comparisons in assembler are hard work. The design of the ASCII codes splits letters into two blocks. That requires your code to …. Read More

ASM Diaries 1: Type Identifier Equals Data Length

A few years ago I reverse engineered Amstrad CPC BASIC. I’m currently writing a compiler for my Pascal-like language (called Quiche). This is an occasional series of articles where I note observations about assembly programming and, in particular, Z80 assembly language. This is a trick I learnt while reverse engineering the Amstrad BASIC interpreter. The …. Read More

Intermediate Language in the Quiche Compiler

[This article is a copy of comments in source code for the Def.IL unit.] The intermediate language (IL) is the core of the Quiche compiler. The parsertakes the source code and converts it to IL. The code generator takes the IL andconverts it to assembly code. Each IL record stores an operation and up the …. Read More

Pico Garry 2350 Part 4: Memory Read Select

Following on from the previous part in this series I now turn to /ROMEN and /RAMRD signals, collectively called Memory Read Select. When the CPU wants to read from memory the gate array has to decide whether that read should come from RAM or ROM. This decision is based on the memory bank being accessed …. Read More

CPC ZERO Part 0: Intro, CPU and ROM

Reverse engineering the Amstrad CPC Revision Zero PCB made me wonder exactly what a 6502 based Amstrad would look like. So I have begin a project, which I’m calling the CPC ZERO, to design such a machine. The prototype PCB is so broken that it doesn’t give much of a starting point for a system, …. Read More

Amstrad CPC Revision Zero: Can It Be Fixed?

I think the genesis of the Amstrad CPC is fairly well known among retro enthusiasts: Amstrad hired some guys to design a machine based around the MOS 6502 processor, but the task was beyond them, Alan Sugar said “You’re Fired”, and a new team, headed by Roland Perry, were hired and came up the the …. Read More

Pico Garry 2350 Part 3: CSIGS (Conditional Signals)

This is the third part of my ‘live blogging’ series as I create a replacement gate array for the Amstrad CPC using a Raspberry Pi RP2350B microcontroller. In this part I work on the /CAS, /244EN and /MWE signals. /244EN and /MWE are only asserted during a fixed portion of the gate array cycle and …. Read More

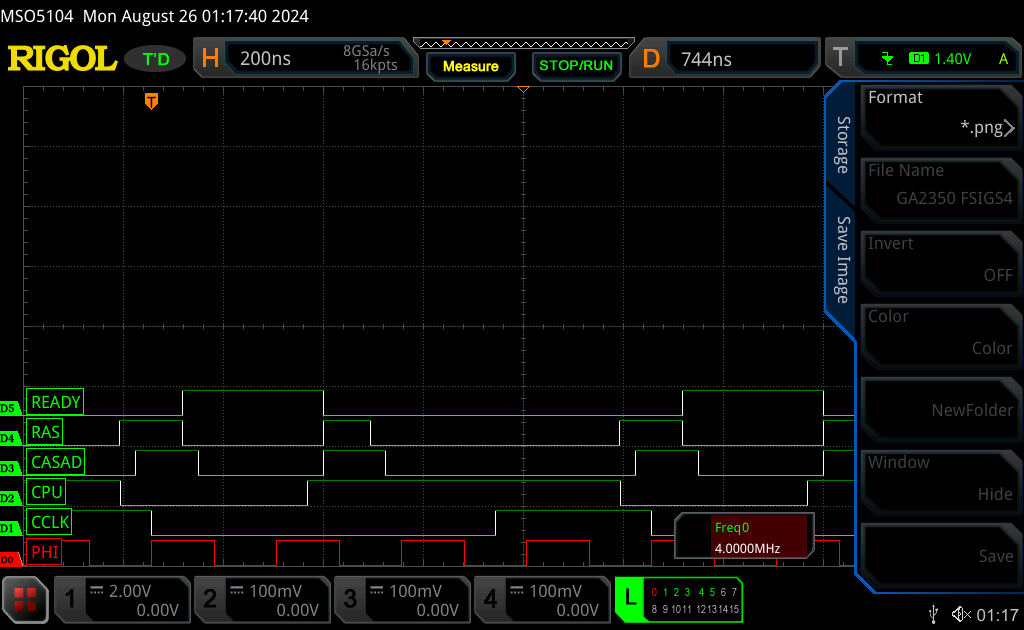

Pico Garry 2350 Part 2: FSIGS (Fixed signals)

This is the second of my development logs as I work to create a replacement for the Amstrad CPC gate array based around a Raspberry Pi RP2350 microcontroller. In the previous article I divided the gate arrays input and output signals into a number of blocks depending on their function. In this article I implement …. Read More